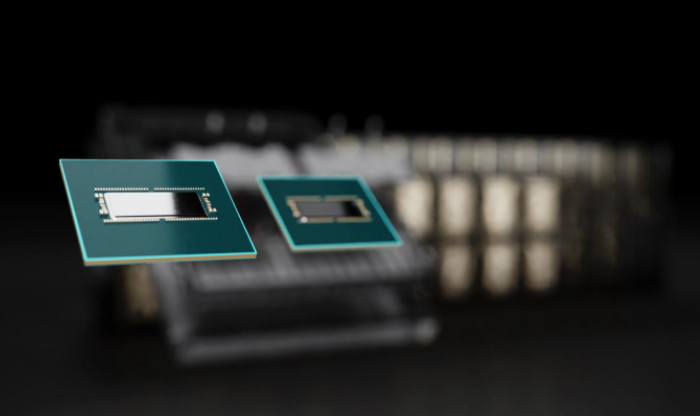

Para lograr una nueva generación de integración a nivel del sistema en los data centers, NVIDIA presentó hoy NVIDIA® NVLink-C2C®, una interconexión ultrarrápida entre chips y entre bloques que permitirá que los bloques personalizados se interconecten de forma coherente con las GPU, CPU, DPU, NIC y SOC de la empresa.

Con el empaquetamiento avanzado, los enlaces de interconexión NVIDIA NVLink-C2C a 900 gigabytes por segundo ofrecerían hasta 25 veces más de eficiencia energética y serían 90 veces más eficientes en el área que PCIe Gen 5 PHY en los chips NVIDIA.

“Es necesario usar chiplets y computación heterogénea para contrarrestar la ralentización de la Ley de Moore”, dijo Ian Buck, vicepresidente de Computación Acelerada de NVIDIA. “Hemos utilizado nuestra experiencia de clase mundial en interconexiones de alta velocidad para desarrollar una tecnología uniforme y abierta que ayudará a nuestras GPU, DPU, NIC, CPU y SoC a crear una nueva clase de productos integrados a través de chiplets”.

NVIDIA NVLink-C2C es la misma tecnología que se usa para conectar chips en la familia de superchips NVIDIA Grace™ , que se anunció hoy, así como para chips basados en la arquitectura NVIDIA Pascal que se anunció el año pasado. NVLink-C2C ahora está abierto para la integración semipersonalizada a nivel de silicio con los chips NVIDIA.

NVIDIA NVLink-C2C es compatible con el protocolo Arm AMBA Coherent Hub Interface (AMBA CHI). NVIDIA y Arm trabajaron en estrecha colaboración para admitir aceleradores totalmente coherentes y seguros, lo que permitirá mejorar AMBA CHI.

“A medida que el futuro del diseño de CPU es cada vez más acelerado y multichip, es fundamental brindar compatibilidad con soC basados en chiplets en todo el ecosistema”, dijo Chris Bergey, vicepresidente sénior y gerente general de la Línea de Negocio de Infraestructura de Arm. “Arm admite un amplio conjunto de estándares de conectividad y diseña nuestro protocolo AMBA CHI para respaldar estas tecnologías futuras, incluida la colaboración con NVIDIA en NVLINK-C2C para abordar casos de uso como la conectividad coherente entre CPU, GPU y DPU”.

NVIDIA NVLink-C2C se basa en la tecnología de diseño SERDES y LINK de clase mundial de NVIDIA, y se puede extender a partir de integraciones a nivel de PCB y módulos multichips a conexiones de obleas e interposer de silicio. Esto ofrece un ancho de banda extremadamente alto al tiempo que optimiza la eficiencia energética y en el área del bloque.

Además de NVLink-C2C, NVIDIA apoyará el estándar Universal Chiplet Interconnect Express (UCIe) que se anunció a principios de este mes. Los clientes podrán usar los diseños SERDES y LINK de clase mundial de NVIDIA para las soluciones de silicio semipersonalizadas que se benefician de la pila de computación de NVIDIA.

Los integradores de silicio personalizados que necesitan baja latencia, mayor ancho de banda o mayor eficiencia energética podrán usar CPU, GPU, DPU, NIC y SOC de NVIDIA para NVLink-C2C o UCIe.